From MegaDrive Development Wiki

Jump to navigation

Jump to search

5313, First version, Old Date Code Format

5313, First version, Old Date Code Format

5313, First version

5313, First version

5313A, Second version

5313A, Second version

5313A-01, Third version

5313A-01, Third version

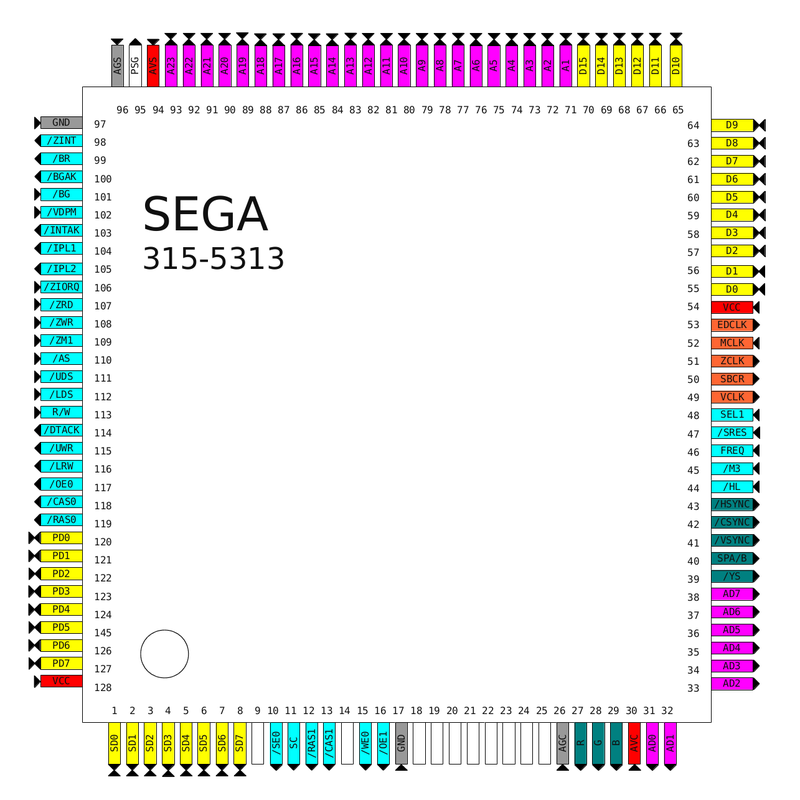

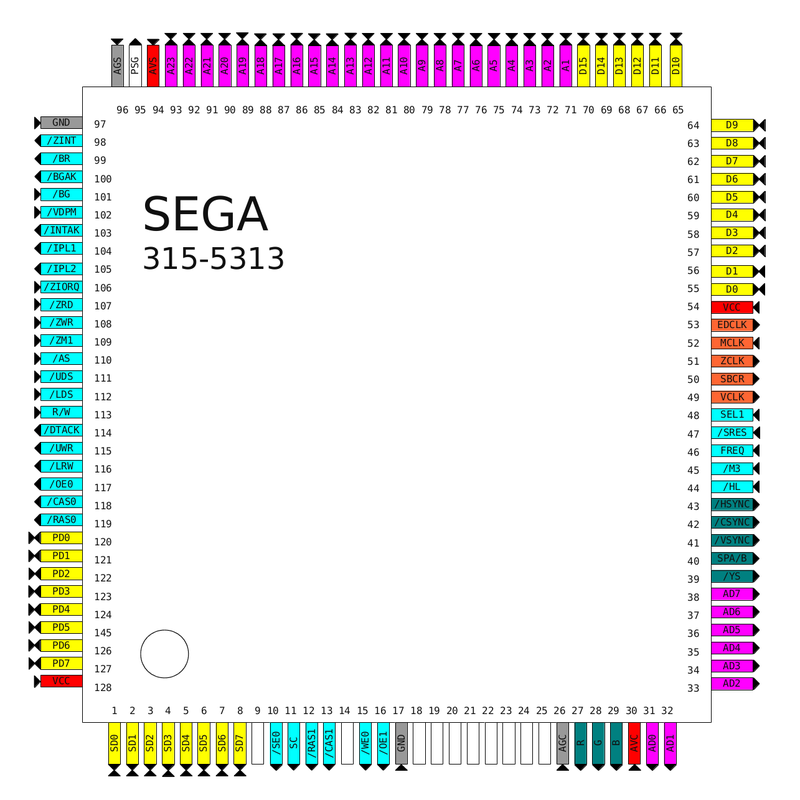

Pinout

Signals

| Address Buses

|

| A1-A23

|

M68K Address Bus

|

| ZA0-ZA15

|

Z80 Address bus

|

| Data Buses

|

| D0-D15

|

M68K Data bus

|

| ZD0-ZD7

|

Z80 Data bus

|

| IO port lines

|

| EM1X

|

Port 1 lines

|

| EM2X

|

Port 2 lines

|

| EM3X

|

Port 3 lines

|

| Control lines

|

| M68K related control lines

|

| /BG

|

Bus Grant

|

| /BGACK

|

Bus Grand Acknowledge

|

| /BR

|

Bus Request

|

| FC0

|

Function Code 0, 1 = Accessing user data

|

| FC1

|

Function Code 1, 1 = Accessing user program

|

| /HALT

|

Halt 68K execution

|

| /RESET

|

Reset 68K

|

| /VPA

|

Valid Peripheral Access

|

| /AS

|

Address strobe

|

| /DTACK

|

Data Acknowledge

|

| /UDS

|

Accessing even bytes

|

| /LDS

|

Accessing odd bytes

|

| R/W

|

Read/Write pin, 0 = write 1 = read

|

| Z80 related control lines

|

| /ZM1

|

Opcode fetch strobe

|

| /ZRD

|

Read strobe

|

| /ZWR

|

Write strobe

|

| /ZMREQ

|

Memory request

|

| /ZIORQ

|

IO request

|

| /ZNMI

|

Non-maskable IRQ

|

| /ZBR

|

Bus request

|

| /ZBAK

|

Bus Acknowledge

|

| /ZRES

|

Reset Z80

|

| /ZWAIT

|

Wait

|

| Address decoding related control lines

|

| /ASEL

|

Read or Write on $000000-$7FFFFF region

|

| /CAS0

|

Read or Write on $000000-$DFFFFF region

|

| /RAS0

|

Read or Write on $E00000-$FFFFFF region, act as /CE signal for the RAM chips

|

| /CE0

|

Chip Enable for the cartridge, low when accessing $000000-$3FFFFF region when expension unit isn't inserted or $400000-$7FFFFF when it is.

|

| /TIME

|

Read or Write on $A13000-$A130FF region

|

| /LWR

|

Lower byte WRite

|

| /UWR

|

Upper byte WRite

|

| /NOE

|

/OE signal for the lower part of the RAM

|

| /EOE

|

/OE signal for the upper part of the RAM

|

| /ZREF

|

Unknown, tied to unused pin #1 of Z80 RAM

|

| /ZRAM

|

/CE for the Z80 RAM

|

| Configuration related control lines

|

| /DISK

|

0V Expansion Unit connected

|

| FREQ

|

5V = 60Hz, 0V = 50Hz

|

| /FRES

|

|

| LANG

|

5V = English, 0V = Japanese

|

| /M3

|

Mark III compatibility mode

|

| VRAM related control lines

|

| /CAS1

|

Column address strobe

|

| /RAS1

|

Row address strobe

|

| /SE0

|

Serial data bus /OE

|

| SC

|

Serial clock

|

| /WE0

|

Write enable

|

| /OE1

|

Output enable

|

| Clock lines

|

| MCLK

|

Master Clock

|

| VCLK

|

68K clock

|

| ZCLK

|

Z80 clock

|

| EDCLK

|

Unknown clock

|